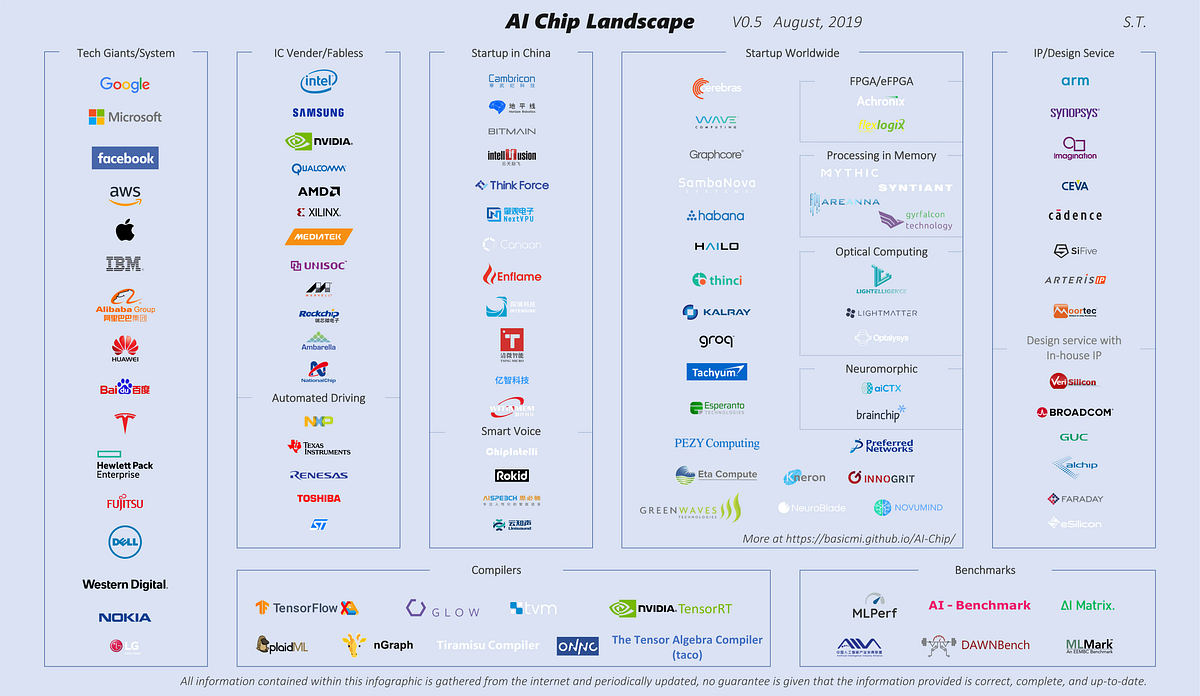

Embedded deep learning creates new possibilities across disparate industries | Vision Systems Design

Arch-Net: A Family Of Neural Networks Built With Operators To Bridge The Gap Between Computer Architecture of ASIC Chips And Neural Network Model Architectures - MarkTechPost

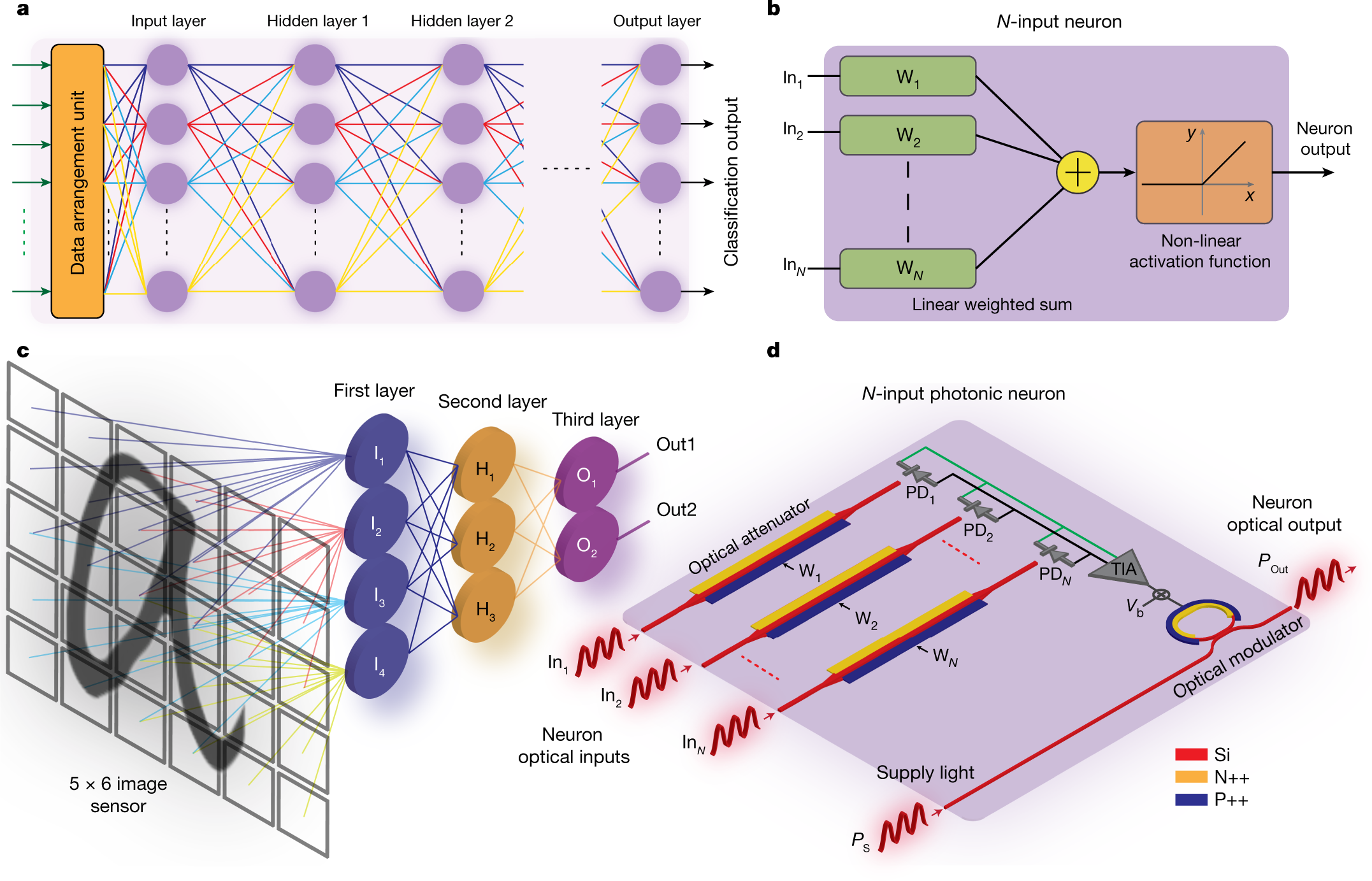

Analog architectures for neural network acceleration based on non-volatile memory: Applied Physics Reviews: Vol 7, No 3

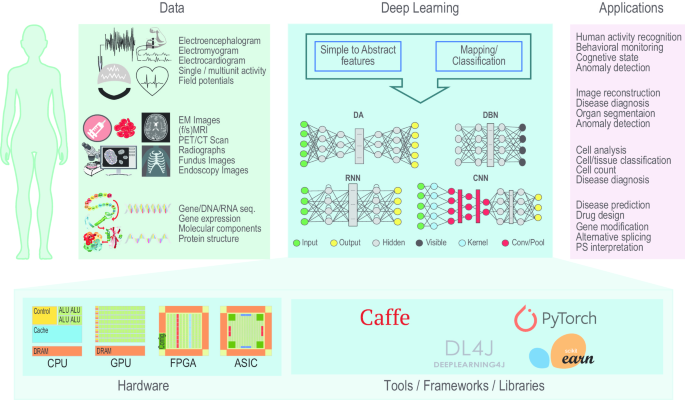

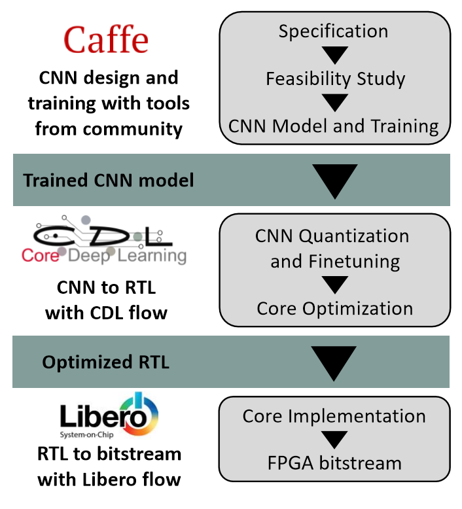

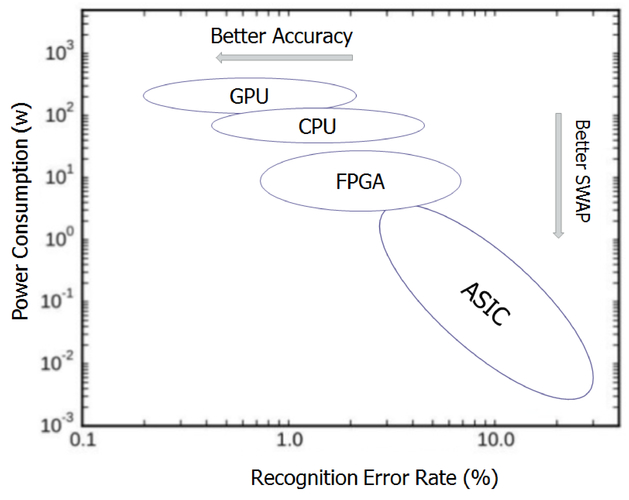

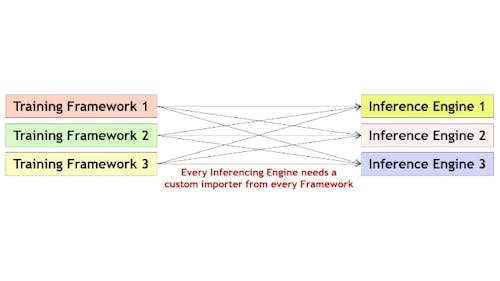

How to Develop High-Performance Deep Neural Network Object Detection/Recognition Applications for FPGA-based Edge Devices - Embedded Computing Design

The New Deep Learning Memory Architectures You Should Know About — eSilicon Technical Article | ChipEstimate.com